Finalizado

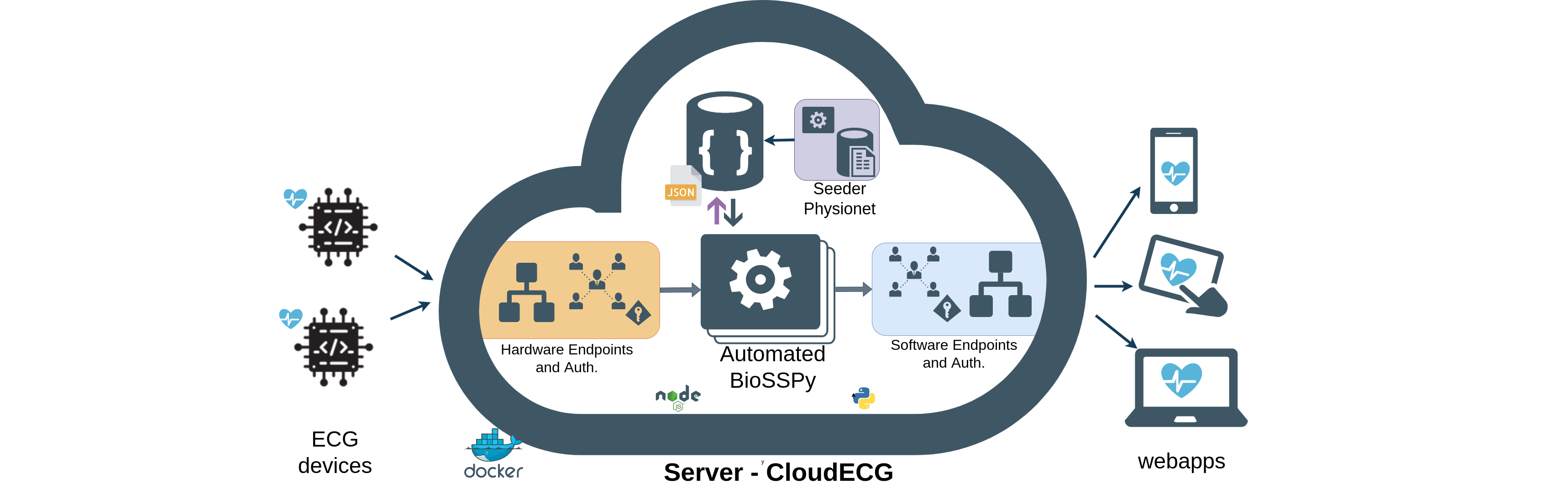

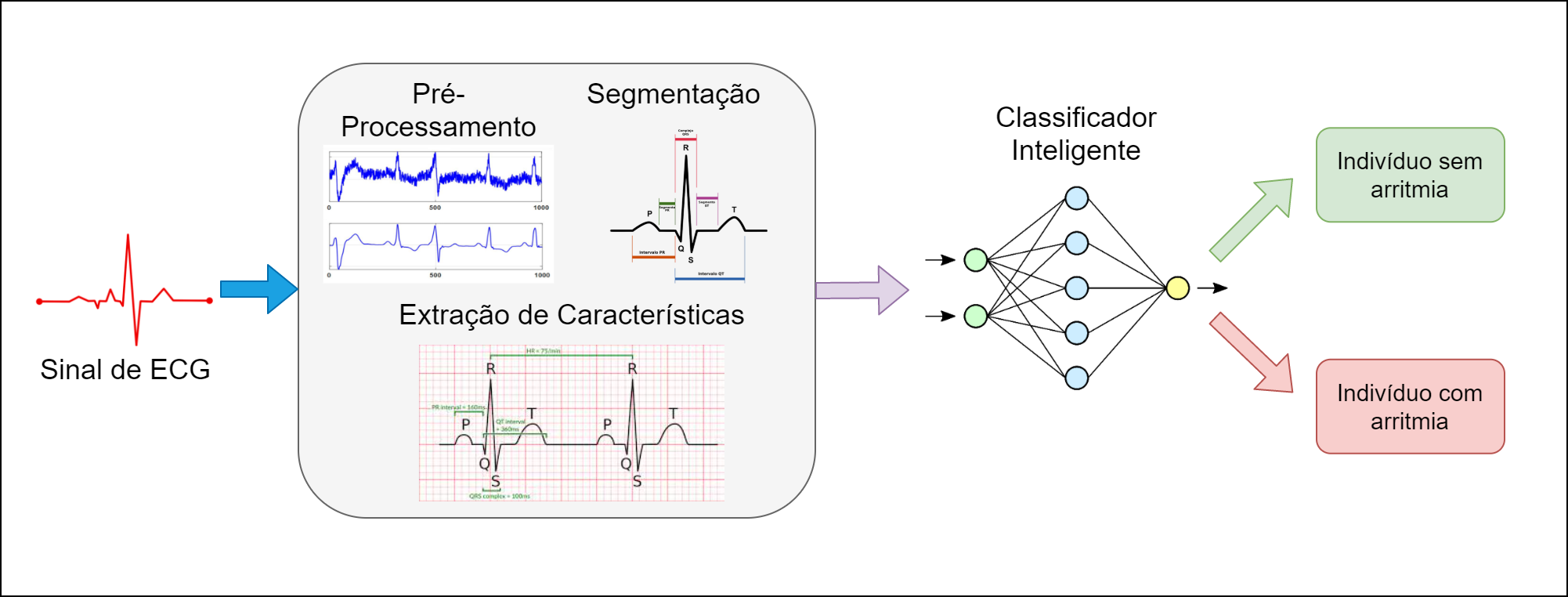

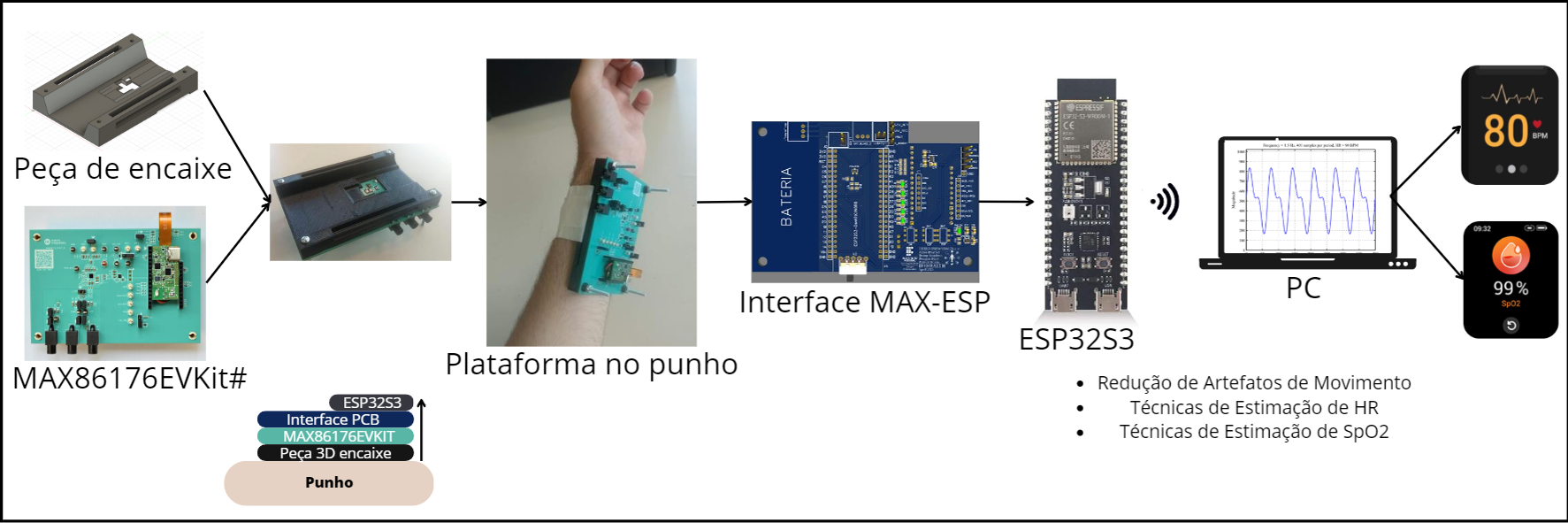

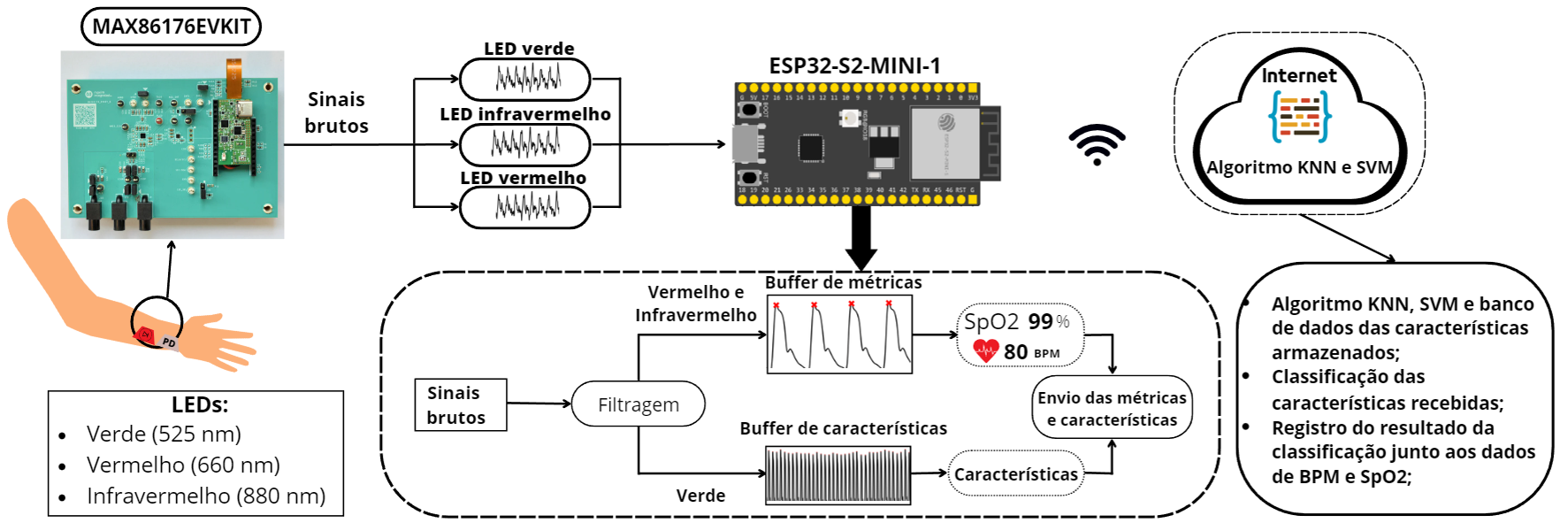

Projeto de pesquisa aprovado no Edital PROPESP 04-2021: NProjeto de pesquisa aprovado no Edital PROPESP 06-2020: No exemplo da figura, na linha de pesquisa IoT in HealthCare, teve alunos da ECA desenvolvendo dispositivo físico para aquisição de sinais de eletrocardiograma (ECG device). O sistema embarcado serve para exibir o ECG localmente e enviar os dados para internet. Também houve alunos do TSI no back-end para armazenamento e processamento do ECG e no front-end para visualização do ECG.

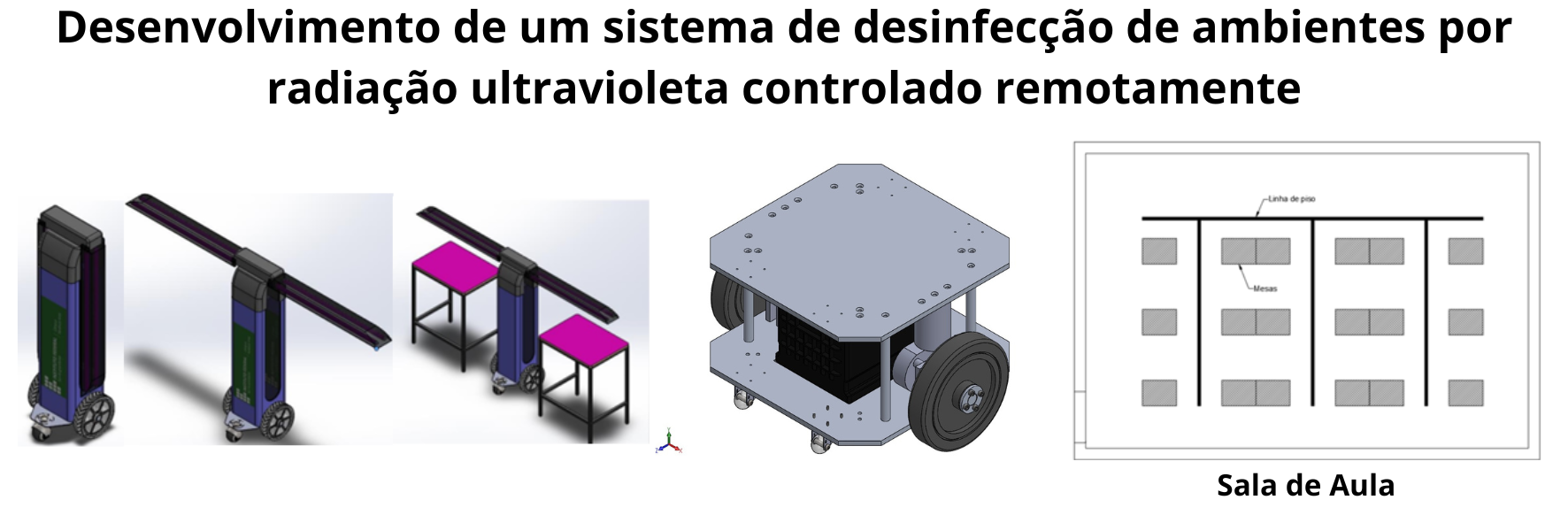

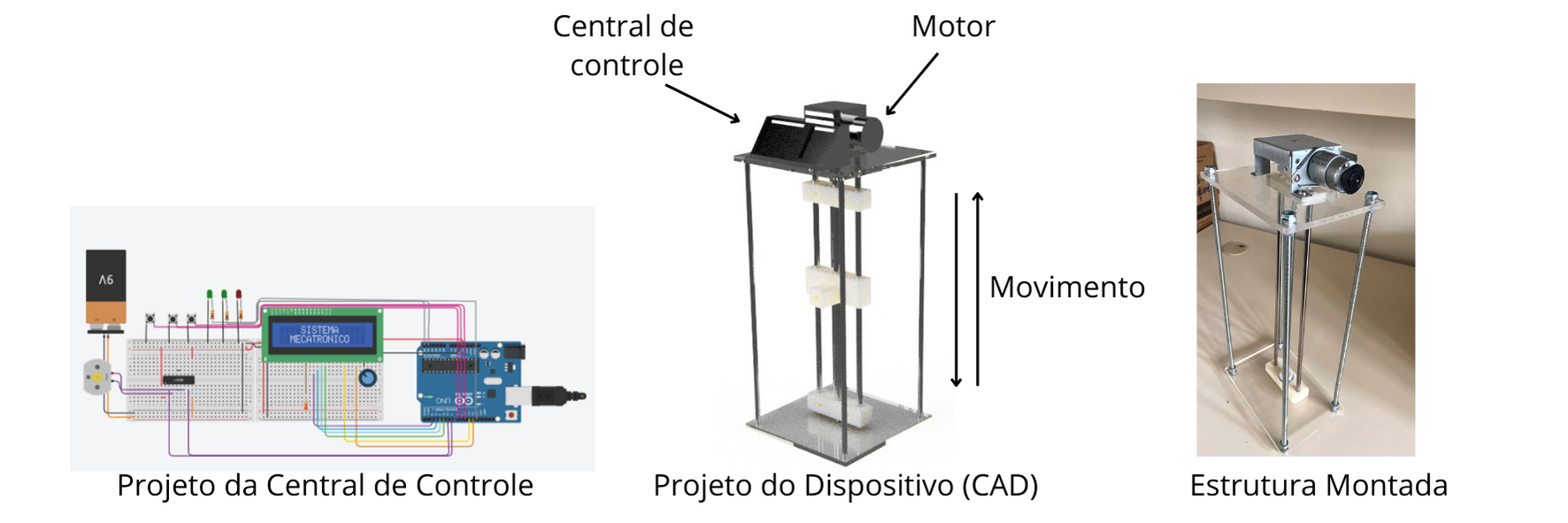

Vigência: AGO/21 até AGO/22

Coordenador: Prof. Fábio Itturriet

Membros: Prof. André Del Mestre e Prof. Juliano Machado

Bolsistas: Patrick Anderson Lacerda Morás (FAPERGS), Job dos Santos Coleraus (FAPERGS) e Marcelo Da Silva Janke (Voluntário)

.png)

.png)

.png)

(2).jpg)